The significance of selecting the "ideal" FPGAs for a design is growing, especially as power consumption becomes a key concern. Effective power management is essential in most applications, and many industry standards now impose power limits on individual cards or entire systems. As a result, designers must address power-related challenges earlier in the development cycle, often starting with the choice of FPGA.

Opting for an FPGA with lower power consumption simplifies board design by reducing the required supply voltage, making power supply and thermal management easier, and lowering the demands on the power distribution network. Additionally, low power consumption extends battery life and improves system reliability, as components operating at lower temperatures tend to last longer.

The power challenge evolves with each new generation of process technology, where transistor sizes shrink according to Moore’s Law. However, this miniaturization leads to increased leakage current, which raises static power consumption—especially when the FPGA is inactive. At the same time, higher performance often means faster clock speeds, increasing dynamic power usage. Static power stems from leakage currents, while dynamic power depends on how frequently the logic and I/O are switching. As FPGA capacities grow, both types of power consumption continue to rise, due to more transistors and higher operating speeds.

Given these factors, designers need a clear understanding of power and thermal issues early in the design phase. Simply adding a heat sink won’t be enough. Therefore, minimizing the amount of logic used in the design becomes crucial.

To reduce power consumption effectively, it's important to follow certain guidelines throughout the design process. Early awareness of these issues can yield the greatest benefits. Figure 1 outlines the key stages of the design process, including FPGA selection and low-power design strategies.

[Figure 1: Reduced power consumption begins with device selection, tool support, and software optimization]

Xilinx 7 Series FPGAs use a 28nm high-performance, low-power (HPL) process that offers significant performance while keeping power consumption low. This helps avoid complex and costly static power management solutions. Although the 28 HP process may not offer the highest performance among 7 Series FPGAs, its static power consumption is less than half that of competing devices, avoiding major leakage problems. As shown in Figure 2, the overall power consumption of 7 Series products is about half that of previous 40nm devices.

[Figure 2: Xilinx 7 Series FPGAs consume only half the power of 40nm process devices]

During development, designers can choose larger FPGAs and then opt for smaller ones during production, which lowers costs and reduces system power. All 7 Series FPGAs share a unified architecture, making it easy to migrate between different devices within the series.

[Table 1: Static, Dynamic Power, and Performance Comparison]

For larger systems, using multiple FPGAs can complicate data transfer between them. Xilinx’s Stacked Silicon Interconnect (SSI) technology addresses this by integrating multiple chips into a single, large device. This approach significantly reduces both static and I/O interconnect power consumption compared to traditional multi-FPGA designs. SSI also enables much higher speeds with lower power usage because all connections are internal.

Xilinx 7 Series FPGAs also offer extended voltage options. For example, -3L and -2L devices support a wider temperature range and can operate at lower voltages, such as 1.0V or 0.9V. Operating at 0.9V reduces static power by around 30%, though it slightly impacts performance. However, Xilinx screens these devices to ensure they meet tighter specifications, allowing them to consume up to 55% less power under worst-case conditions.

Reducing VCCINT by 10% can lead to a 20% reduction in dynamic power, further enhancing efficiency.

Xilinx provides several tools to help estimate and analyze power consumption during the design process. The XPower Estimator (XPE) allows early power estimation before any design implementation. PlanAhead helps estimate power at the RTL level, offering more detailed insights than XPE. Finally, the XPower Analyzer (XPA) provides post-layout analysis, giving precise information on power and heat generation across various modules.

These tools enable designers to identify the most power-hungry components and optimize their designs accordingly, ensuring efficient and reliable FPGA implementations.

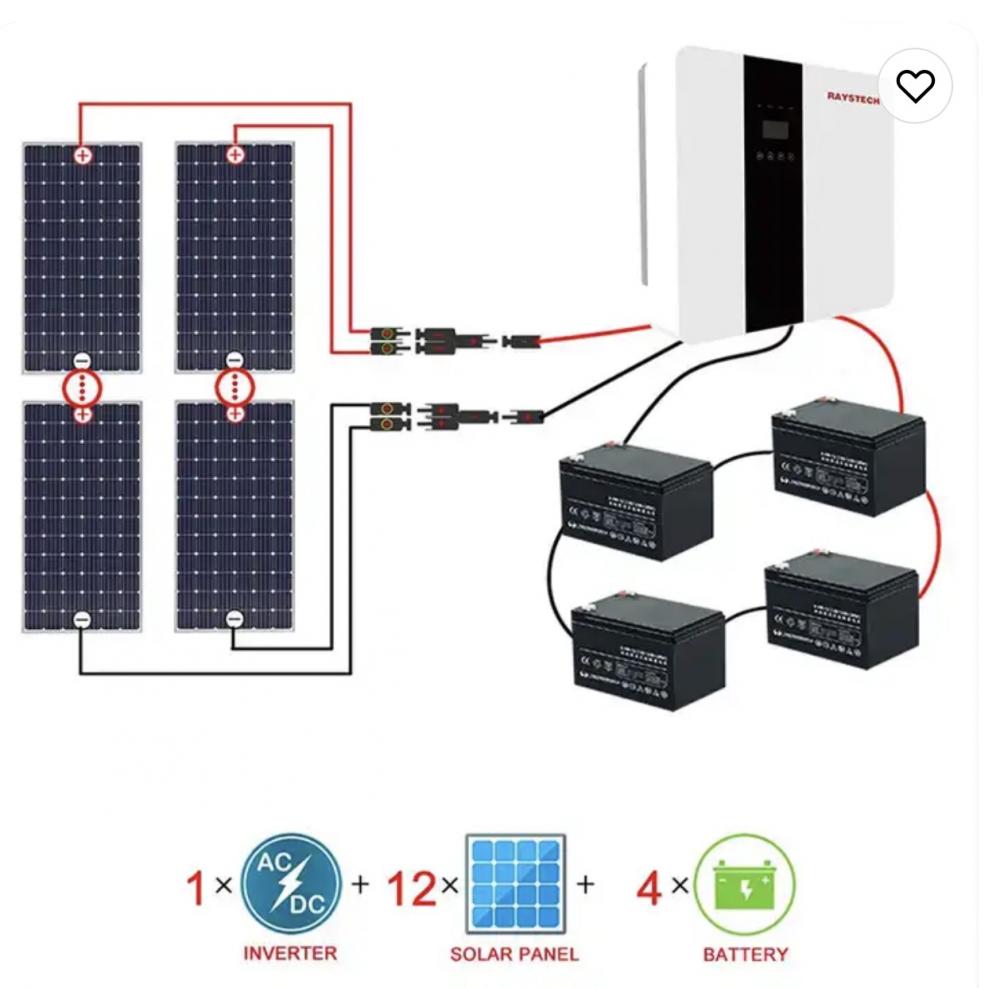

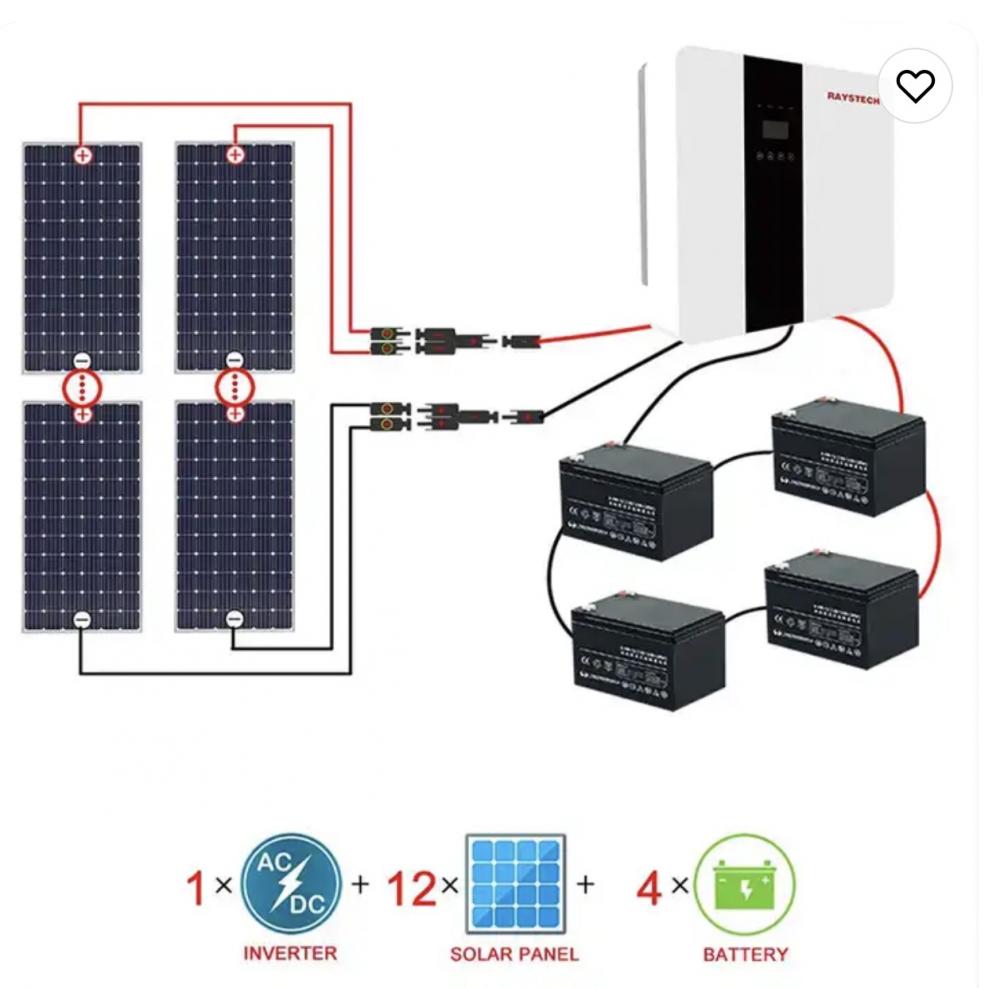

Solar Engergy System

Solar energy system, off gird pv system, grid pv system, solar power system, Solar Panel system, on grid solar system, grid tied solar system,20kw solar system

Solar energy system include Solar photovoltaic system: 1. Off grid photovoltaic system mainly consists of solar modules, controllers, and batteries. To supply power to AC loads, it is also necessary to configure an AC inverter. 2. Grid connected photovoltaic power generation system. 3. Distributed photovoltaic power generation system. Distributed power generation or distributed energy supply.

|

solar cell type

|

mono crystalline, half cut cell

|

|

solar energy pv system include

|

on grid system, off grid system, hybrid system

|

|

solar configuration

|

solar panel, inverter, battery, bracket cabels, mc4 connector

|

|

|

Product details and pic

Solar Engergy System,Gird Solar Power System,Pv System For Carport,Energy System Off Grid Solar System

PLIER(Suzhou) Photovoltaic Technology Co., Ltd. , https://www.pliersolar.com