In recent years, through-silicon via (TSV) technology has advanced rapidly, offering significant benefits such as low power consumption, compact form factor, high performance, and high stacking density. This technology has gained widespread industry recognition and is seen as a key enabler for continuing Moore's Law. In this article, the author provides an overview of the TSV process flow and key technologies, including critical steps like etching, separation, metal filling, and copper exposure.

1. Overview

Three-dimensional integrated circuits (3D ICs) are considered promising solutions to overcome the limitations of Moore’s Law due to their low power consumption, small size, high performance, and high stacking density. Achieving 3D integration requires several essential technologies, such as through-silicon vias (TSVs), wafer thinning, and wafer/chip bonding. TSV interconnects offer advantages like shorter signal paths and smaller package sizes, making them a core technology in 3D integration. TSV technology can be categorized into three types: through-hole processing before the CMOS process, through-hole processing during the CMOS and back-end-of-line (BEOL) processes, and back via processing after the CMOS process but before wafer thinning. The choice of method depends on specific production requirements.

TSV technology has found applications in various products, including MEMS, mobile devices, CMOS image sensors (CIS), bio-applications, and memory chips. Despite the existing research and achievements, TSV technology is still not widely adopted due to its relatively high cost. In this paper, the authors review the TSV process flow, focusing on deep reactive ion etching (DRIE) for via fabrication, insulation layer deposition, barrier and seed layer formation, via filling, and chemical mechanical polishing (CMP). Key processes such as copper exposure are also discussed in detail.

2. TSV Structure and Manufacturing Process

2.1 TSV Structure

The TSV structure consists of processed through-holes in a silicon wafer, with electroplated copper pillars, an insulating layer, and a barrier layer arranged from the inside out. The insulating layer serves to isolate the silicon from the conductive material, typically made of silicon dioxide. However, due to potential diffusion of copper atoms through the insulating layer, a barrier layer—usually a chemically stable metal—is added between the copper and the insulator. Initially, tungsten was used as the filling material due to its low thermal expansion coefficient, but copper has since become the preferred material due to its superior conductivity.

2.2 TSV Manufacturing Process

The TSV manufacturing process involves the following steps:

(1) A photoresist is applied to define the etched area, followed by deep reactive ion etching (DRIE) to create a blind via on one side of the silicon wafer.

(2) A silicon dioxide (SiOâ‚‚) insulating layer is deposited, along with a titanium (Ti) barrier layer and a copper (Cu) seed layer using physical vapor deposition (PVD).

(3) Electroplating is used to fill the via with copper.

(4) Excess copper is removed using chemical mechanical polishing (CMP).

(5) A redistribution layer (RDL) is formed on the side of the wafer with the blind via.

(6) The RDL is bonded to a carrier wafer using a sol.

(7) The other end of the copper column is exposed using CMP and back grinding.

(8) A copper under bump metallization (UBM) is fabricated on the backside of the wafer.

(9) Microbumps are then created on the backside.

(10) The wafer with microbumps is separated from the carrier, and the sol is removed from the front side.

3. Key Technologies in TSV Production

3.1 TSV Etching

TSV etching is a critical step in 3D integration. The Bosch etching process is commonly used for deep silicon etching, offering high etch rates (5–10 μm/min) and good selectivity. However, this process can lead to rough sidewalls, which may cause issues in subsequent steps, such as leakage and reliability problems. As TSV dimensions shrink, minimizing sidewall roughness becomes increasingly important.

3.2 TSV Insulation

An insulating layer is essential for electrically isolating the silicon substrate. Common materials include SiO₂ or Si₃N₄, deposited via PECVD or SACVD. For smaller TSV diameters (<3 μm), atomic layer deposition (ALD) is preferred due to its better step coverage and lower thermal budget.

3.3 TSV Barrier Layer and Seed Layer

A barrier layer is deposited to prevent copper diffusion during annealing. Materials like Ti, Ta, TaN, and TiN are commonly used. Physical vapor deposition (PVD) is often employed, though it may have limited step coverage for high aspect ratio TSVs. Chemical vapor deposition (CVD) offers better uniformity but requires higher temperatures. Copper seed layers are typically deposited via PVD, and alternative methods like electroless plating are being explored to improve coverage.

3.4 TSV Filling

There are three main methods for copper filling: conformal plating, bottom-up sealing bump plating, and superconformal plating. Each method is suited for different applications and TSV aspect ratios. Conformal plating is similar to standard wafer-level packaging, while bottom-up plating helps avoid voids. Superconformal plating is ideal for larger TSVs and equipment applications. Optimization techniques, such as pulse reverse current (PPR) and anode position adjustment, help reduce filling time and improve efficiency.

3.5 TSV Copper Exposure

Thermal mismatch between copper and silicon can cause reliability issues, such as cracking and delamination. Annealing processes and CMP are used to manage these effects. Proper pre-annealing and copper removal are crucial for long-term stability.

4. Conclusion

This paper reviews various TSV manufacturing techniques in 3D integration, highlighting the development of processes, copper filling methods, and the use of dielectric, barrier, and seed layers to address challenges like silicon sidewall roughness and high aspect ratios. Wet processes help mitigate copper seed discontinuities, while three plating methods—conformal, bottom-up, and superconformal—are available for different applications. TSV gaps can cause electrical failures, and understanding their root causes is essential. With its advantages of compact size, high density, and cost-effectiveness, TSV technology holds great promise for future 3D integration solutions.

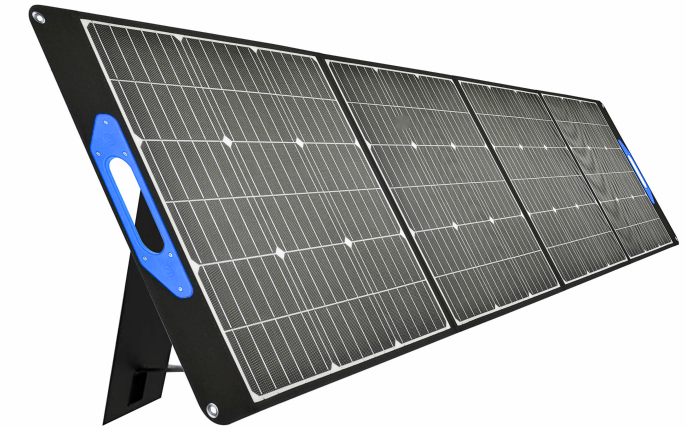

A solar cell panel, solar electric panel, photo-voltaic (PV) module, PV panel or Solar Panel is an assembly of photovoltaic solar cells mounted in a (usually rectangular) frame, and a neatly organised collection of PV panels is called a photovoltaic system or solar array. Solar panels capture sunlight as a source of radiant energy, which is converted into electric energy in the form of direct current (DC) electricity.

200W Solar Panel,Solar Panel Portable Charger,Folding Solar Portable Power Station With Solar Panel,Folding Solar Panel

suzhou whaylan new energy technology co., ltd , https://www.xinlingvideo.com