In the development process of the home fire alarm system project, the author needs to frequently access the operating data with the slave MCU when performing master-slave communication and slave self-task processing. In the past, the traditional method was to externally EEPROM on the MCU or to divide some memory cells inside the MCU to access the running data. The disadvantages of these two methods are: the external EEPROM needs to increase the MCU and EEPROM read and write interfaces, increase the MCU's pin burden, slow down the data read and write speed and increase the power consumption; specifically for running data Dividing the storage unit reduces the storage space of the program code, and the operation of reading, writing, erasing, etc. of the storage space is troublesome, and it is also very careful to prevent the useful program code from being erased.

Renesas RL78 series MCU embedded 2KB DATA FLASH, eliminating the need for users to separately expand data FLASH. The RL78 series MCU also supports BGO operation, and the program instructions can still be executed normally when reading and writing DATA FLASH. Its write operation life on DATA FLASH memory cells is more than 1 million times, which is very suitable for applications that require frequent access to data.

Unlike some semiconductor manufacturers' control chips, Renesas does not directly open the DATA FLASH read and write operations to the user, but provides a software interface called PFDL (Pico Data Flash Library). To achieve the operation of the flash system. When the user uses it, he only needs to call the corresponding library function to perform operations such as reading, writing, verifying, and erasing the DATA FLASH without having to care about the specific implementation of the underlying driver function. This greatly facilitates the design of the user program and shortens the development cycle.

1) DATA FLASH structure and PFDL

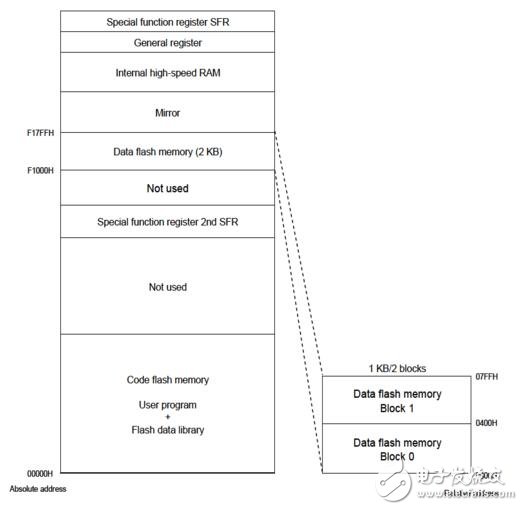

The storage junction of the RL78 is shown in Figure 1. The physical address of the Data Flash memory is F1000H-F17FFH, which is divided into two BLOCK areas, each of which is 1 KB in total, 2 KB in total.

Figure 1: Storage structure of Renesas RL78 series MCU

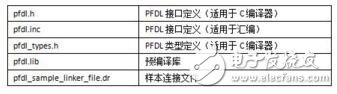

The PFDL consists of the library files shown in Table 1.

Table 1: PFDL library files

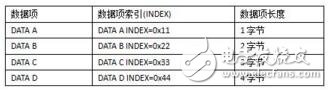

2) Data Flash storage structure and usage

First of all, it is necessary to explain several problems of the RL78 series MCU on DATA FLASH operation. The RL78 series DATA FLASH erase operation can only be in BLOCK unit and does not support single word or single byte erase. Therefore, when a data with a length of several bytes is to be written to the DATA FLASH, it is impossible to write the data to the storage unit corresponding to the fixed physical address each time, but must be written in the new empty storage unit. . This means that users must have addressing capabilities when designing the DATA FLASH memory structure.

RL78 series DATA FLASH can only have one BLOCK active at the same time, which is valid. At this time, another BLOCK is inaccessible and invalid. Conventionally, we often refer to a BLOCK of DATA FLASH as a page. When a valid page is filled with data, if you want to continue writing data, you can only write it on the next page, and you need to add the previous one. The other data items useful in the page are copied to the next page, and the next page is marked as the current valid page, and the previous page is marked as an invalid page, that is, there must be a DATA FLASH page mark and a page guide mechanism.

To this end, the author divides the entire DATA FLASH into two pages (each BLOCK naturally forms one page, two pages alternately use), and the starting address of each page serves as a page marking unit, as shown in Table 2. The tag unit should be read to confirm the currently valid page before each DATA FLASH operation.

Table 2: Page Markers

Usually,10 & 20 layers PCB are HDI board,but some are not .Some with big trace width and space,holes are over 0.3mm too. We have much experience in doing 10 layer PCB & 20 layer PCB.

A ten-layer board should be used when six routing layers are required. Ten-layer boards, therefore, usually have six signal layers and four planes. Having more than six signal layers on a ten-layer board is not recommended. Ten-layers is also the largest number of layers that can usually be conveniently fabricated in a 0.062" thick board. Occasionally you will see a twelve-layer board fabricated as a 0.062" thick board, but the number of fabricators capable of producing it are limited..

High layer count boards (ten +) require thin dielectrics (typically 0.006" or less on a 0.062" thick board) and therefore they automatically have tight coupling between layers. When properly stacked and routed they can meet all of our objectives and will have excellent EMC performance and signal integrity.

A very common and nearly ideal stack-up for a ten-layer board is shown in Figure 12. The reason that this stack-up has such good performance is the tight coupling of the signal and return planes, the shielding of the high-speed signal layers, the existence of multiple ground planes, as well as a tightly coupled power/ground plane pair in the center of the board. High-speed signals normally would be routed on the signal layers buried between planes (layers 3-4 and 7-8 in this case).

10 layer PCB 10 layer TG170 PCB 10 layer design

Storm Circuit Technology Ltd , https://www.stormpcb.com