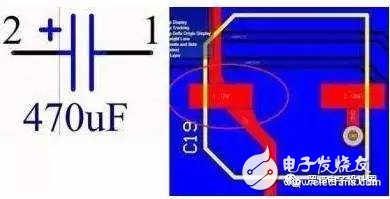

1. Is there a polarized capacitor, and are the schematic and PCB reversed?

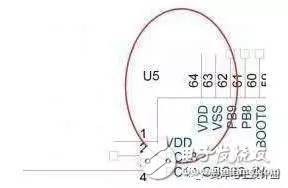

2. The power supply and ground connections were forgotten—there's also a polarity issue.

3. The connector’s wiring order is reversed.

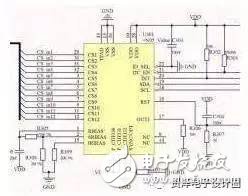

4. RX and TX are reversed.

When drawing the serial port RX and TX, make sure not to reverse them. If you do, the board will come back for testing, but the serial communication won’t work.

5. I created a package, but the device wasn’t available. I downloaded the datasheet from Baidu, but couldn’t find a supplier for it.

6. I directly copied a circuit, but ended up with components that couldn’t be purchased.

Once, a team made a smart lock by copying Samsung’s design. However, they struggled to find a capacitive touch controller in Korea, with no local agent or support. They had to test and troubleshoot on their own.

7. When choosing a capacitor, I only considered the capacitance value, not the voltage rating. As a result, the large package couldn’t fit the required capacitor.

8. When selecting a resistor, I only looked at the resistance value and ignored the power rating.

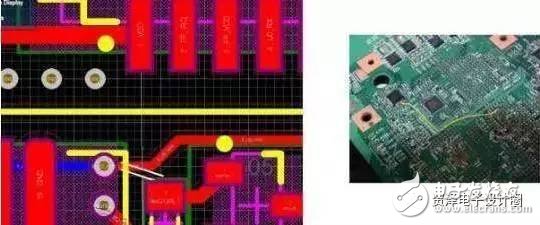

9. After finishing the PCB layout, I didn’t check the DRC report. I just relied on my eyes to spot flying traces. When the board came back, it actually had short circuits.

At one point, I turned off the DRC for short-circuit checks, and as a result, the power supply had reversed polarity.

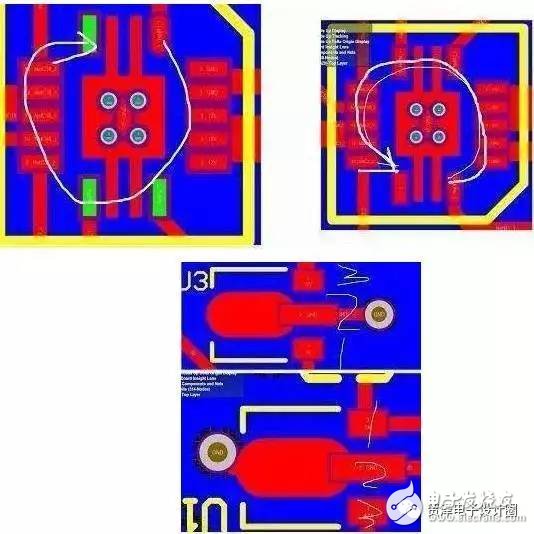

10. The package was mirrored.

Back then, I was in a rush. I didn’t get the chip, so I just followed the datasheet to draw the footprint and sent the board out. When it arrived, I saw the mirrored package. But this isn’t entirely my fault, because the datasheet showed a bottom view without specifying it!

11. The thermal pad’s solder mask wasn’t properly processed.

12. The LM1117 was drawn incorrectly, and the INA826’s pinout was also wrong in the schematic. When I burned the firmware, I forgot to select the external crystal, and after spending a long time debugging, I realized I had missed that step.

13. The 431 regulator is tricky. I always double-check the pin order every time.

Regarding the SOT23 package of the 431 regulator, the pin arrangement is consistent across manufacturers. However, TI’s TL431A uses a CAR configuration, while UTC’s TL431A and CJ431A use RAC. Some even have different pin arrangements. The datasheets usually show a bottom view, which can lead to incorrect placement if the layout isn’t mirrored.

14. I once reversed the package according to the datasheet and claimed it was the most beautiful layout I had ever done.

15. Every time a board has a daughter card, I end up sweating and worrying all night.

16. The battery interface was reversed, and it cost me dearly.

Common Eight Misunderstandings in Circuit Design

Phenomenon 1: The PCB design requirements are low, so just use thin lines and auto-route.

Comment: Auto-routing takes more space and creates more vias than manual routing. In mass production, PCB manufacturers often reduce costs based on line width and via count, affecting yield and drill bit usage. This is why some suppliers offer lower prices.

Phenomenon 2: These bus signals are pulled with resistors, and I feel relieved.

Comment: Not all signals need pull-ups. For simple inputs, pull-down resistors are sufficient, consuming only tens of microamps. However, if a signal is driven, current can reach milliamperes. For example, a 32-bit address/data bus with pull-up resistors on 244/245 isolated signals can consume several watts.

Phenomenon 3: What should I do with these unused CPU and FPGA I/O ports? Just leave them empty for now.

Comment: Leaving them floating may cause oscillations due to interference. MOS devices consume power based on gate flips. Pulling them up adds microampere currents, so the best approach is to set them as outputs (without connecting other driven signals).

Phenomenon 4: There are many unused logic gates in this FPGA—let’s use them.

Comment: FPGA power consumption depends on the number of flip-flops used and switching activity. A single model can vary by 100 times depending on the design. Reducing flip-flop usage is key to lowering power consumption at high speeds.

Phenomenon 5: These small chips consume very little power, so no need to worry about it.

Comment: Even small chips can have high power consumption based on pin current. An ABT16244 draws less than 1 mA without load, but each pin can drive 60 mA. At 16 pins, that’s up to 960 mA—enough to cause heat issues.

Phenomenon 6: This memory has many control signals. I only need OE and WE; grounding CS makes reading faster.

Comment: Most memory power is consumed when the chip select (CS) is active, regardless of OE and WE. Using CS to control the chip as much as possible, and narrowing its pulse width when possible, can significantly reduce power consumption.

Phenomenon 7: Why do these signals have overshoot? Just match them well, and it’ll go away.

Comment: Overshoot is common except for specific signals like 100BASE-T or CML. If it’s not too bad, matching might not be necessary. TTL output impedance is under 50 ohms, sometimes as low as 20. Using large matching resistors would cause excessive current and poor signal levels. It’s hard to perfectly match TTL, LVDS, or RS422 signals, so acceptable overshoot is often fine.

Phenomenon 8: Reducing power consumption is the hardware engineer’s job—it has nothing to do with software.

Comment: While hardware sets the stage, software plays a big role. Almost every chip access and signal flip is controlled by software. Optimizing code to reduce external accesses, using internal cache, and responding to interrupts promptly can greatly reduce power consumption.

Audio And Video Cable,Audio Video Cables,Hdtv Data Cable,Optique Audio Cable

ShenZhen Puchen Electronics Co., Ltd. , https://www.szpuchen.com